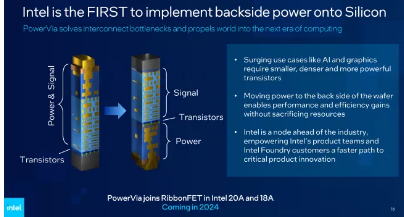

英特尔周一详细介绍了其背面供电网络 (BS PDN) 的实施,该网络将成为其 英特尔 18A 和 20A(18/20 埃,1.8/2.0 纳米级)制造工艺的一部分。此外,该公司还透露了更多有关该技术为其专为最佳 BS PDN 而设计的内部 Intel 4 + PowerVia 节点提供的优势的信息。

英特尔的 18A 和 20A 制造技术将引入两项关键创新:RibbonFET 环栅场效应晶体管 (GAAFET) 和 PowerVia 背面供电网络。GAA 晶体管的优势之前已经讨论过,但不在今天发布的范围之内。我们将专注于背面供电。

背面电源轨旨在分离电源和 I/O 布线,将电源线转移到晶圆背面。这种方法解决了诸如后端线路 (BEOL) 中通孔电阻增加等问题,最终提高了晶体管的性能并降低了它们的功耗。它还消除了数据线和电源线之间的任何可能干扰,并增加了逻辑晶体管密度。

随着时间的推移,BD PDN 将成为标准芯片功能,但目前英特尔认为这是一项重大突破性创新,类似于 2003 年 90 纳米的应变硅、2007 年 45 纳米的基于铪的高 K 金属栅极以及 2012 年的 22 纳米 FinFET .

英特尔表示,当在内部工艺节点的测试芯片中实施时,其背面 PDN 使其能够将时钟速度提高 6% 以上,将 IR 电压降降低 30%,并提高其 E-core 芯片大面积的单元利用率到 90% 以上。尽管有这些好处,但由于多种原因,实施和构建背面供电仍是一项挑战。

构建 PowerVia 背面 PDN

构建背面 PDN 与传统的正面供电截然不同。如今,即使是最先进的芯片的生产也非常简单。每个晶圆的制造都从最复杂的 M0 晶体管层开始,间距小至 30 纳米(对于英特尔 4 节点),使用最复杂的制造工具,如 EUV 扫描仪。然后芯片制造商在第一个晶体管层之上构建不太复杂的晶体管层,逐渐增加尺寸,因为他们需要连接所有层并为所有晶体管供电。